www.188betkr.com 讯在半导体先进封装领域,随着多芯片集成与异构集成需求的不断攀升,传统基板材料逐渐难以满足高密度互连、结构稳定性等核心要求。玻璃基板凭借独特的材料性能与工艺潜力,正成为突破封装技术瓶颈的重要解决方案,其在结构设计、制造流程及高密度互连技术上的创新,为高性能芯片封装提供了新路径。

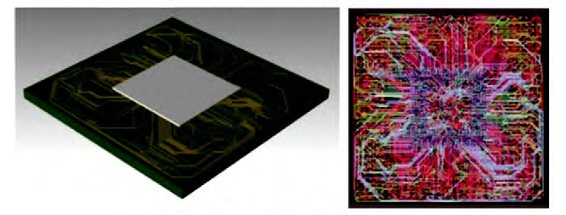

玻璃基板的核心竞争优势源于其独特的封装结构设计。该结构以玻璃为核心层材料,在核心层上下表面构建高密度、细间距金属布线,布线通过电镀铜或钨填充形成,细间距区域则采用薄膜沉积氧化硅作为介质层实现绝缘。这种设计可实现比传统基板更精细的线宽线距与更高的布线密度,为多芯片间局部高密度互连提供支撑。同时,玻璃基板支持通过倒装方式实现芯片与基板金属焊盘的互连,还能在基板内部集成电阻、电容、电感等无源组件,进一步提升封装集成度。

从材料性能对比来看,玻璃在关键参数上显著优于传统基板材料,其表面粗糙度低于10nm,热膨胀系数可在3×10-6~9×10-6K-1之间灵活调节,杨氏模量达50~90GPa,且吸湿性接近于零。这些特性使其在微细布线加工、热应力控制及结构稳定性方面表现突出,有效解决了传统有机材料层压板(如BT、ABF类)在高精度封装中的短板。

在封装尺寸上,玻璃基板可实现100mm×100mm的大尺寸加工,为多芯片集成与系统级封装(SiP)设计提供了更大空间。此外,玻璃面板在面积利用率上的优势也十分显著,515mm×510mm、650mm×550mm规格的玻璃面板,有效面积分别是12英寸硅晶圆的3.6倍与4.9倍,大幅提升了单位产能与封装效率,为芯粒整合创造了有利条件。

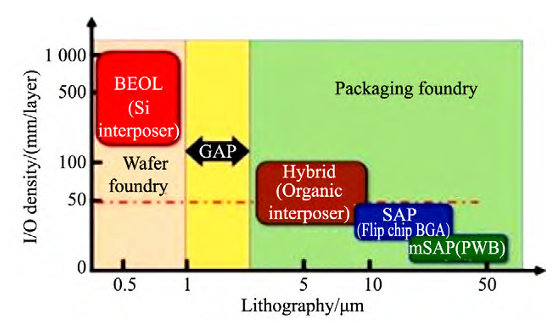

在高密度互连技术领域,玻璃基板已形成多类成熟工艺方案,以匹配不同精度需求。当前主流工艺可分为以下三类:

硅基半加成工艺:以TSMC、ASE、Intel为代表,核心是在晶圆表面制备重布线层(RDL)。流程为溅射钛/铜黏附层与种子层,旋涂PR光刻胶(如JSR111)并曝光露出电镀区域,最终通过电镀、湿法去胶、湿法刻蚀完成线路制作。该工艺对种子层黏附性、电镀均匀性、药液交换效率要求较高,成本相对较低,适用于线宽/线距≥5μm/5μm的产品。

无机介质层大马士革工艺:以Amkor为代表,专注于亚微米级金属布线。先沉积无机介质层并开窗,再整面电镀金属,最后通过化学机械抛光(CMP)去除覆铜层。金属布线嵌入介质层的设计可增强与基材结合力,为实现线宽/线距≤2μm的细间距RDL提供解决方案。

半导体硅基精密工艺:依托半导体硅工艺技术,通过剥离、离子束刻蚀(IBE)、沟槽加工等技术实现精密图案化。可将线宽与线距均控制在≤2μm,显著提升互连密度,但对生产条件、设备配置、制造尺寸要求严苛,导致成本较高。

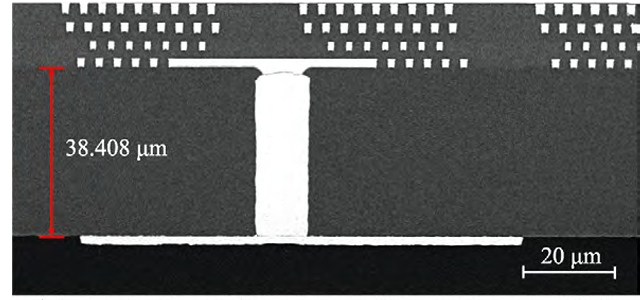

玻璃表面布线加工路线及高密度布线样品 来源:《玻璃基板技术研究进展》(赵瑾等)

行业实践已验证玻璃基板在高密度互连领域的应用潜力。台积电利用数字光刻与低温溅射技术,在37cm×47cm玻璃基板上成功堆叠5层RDL,最小线宽达3μm,采用PSPI聚合物作为介质层,侧壁倾角约71°,翘曲控制在0.2mm以内;厦门云天半导体则通过大马士革工艺,在玻璃正面制备出5层无机薄膜介质的RDL互连堆叠结构,最细线宽可达1.5μm。这些成果表明,玻璃基板可通过TGV(玻璃通孔)实现垂直互连,配合高密度RDL满足高I/O、高带宽的封装需求。

最小RDL线宽为1.5μm的5层RDL堆叠结构 来源:云天半导体

随着人工智能、高性能计算领域对芯片算力的需求持续攀升,先进封装技术正朝着高集成度、高可靠性的方向加速演进。在此趋势下,玻璃基板凭借材料性能、工艺灵活性与集成潜力的综合优势,有望在未来半导体封装领域占据更关键的地位。

参考来源:

赵瑾.玻璃基板技术研究进展

张兴治.玻璃基板在芯片封装中的应用和性能要求

刘丽敏.基于超薄玻璃衬底的桥连封装技术研究

(www.188betkr.com 编辑整理/月明)

注:图片非商业用途,存在侵权告知删除!